16/32-bit ARM microcontrollers; 8 kB cache, up to 1 MB flash, Hi-Speed USB 2.0 device, and SDRAM memory interface

Rev. 03 — 17 April 2008

**Preliminary data sheet**

### 1. General description

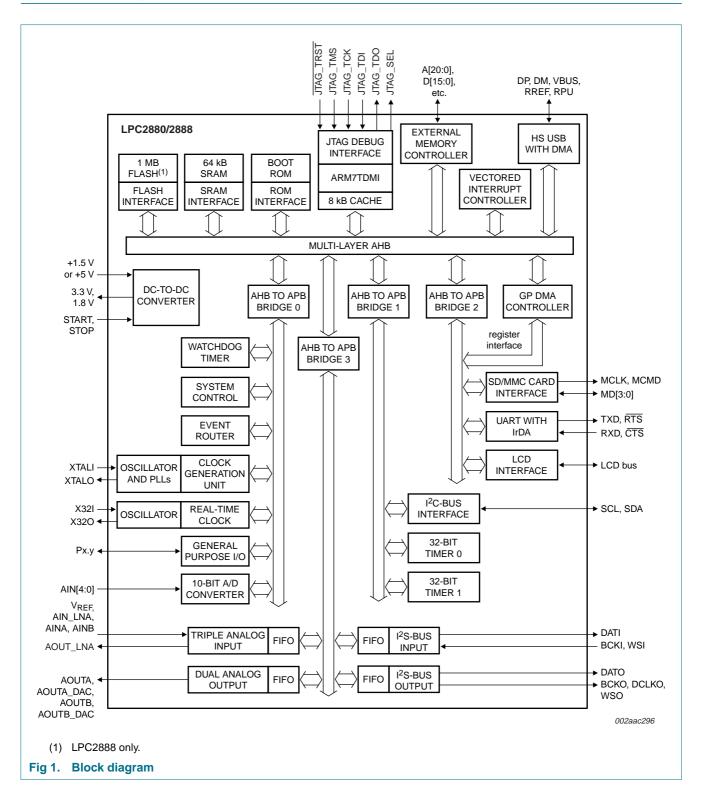

The LPC2880/2888 is an ARM7-based microcontroller for portable applications requiring low power and high performance. It includes a USB 2.0 Hi-Speed device interface, an external memory interface that can interface to SDRAM and flash, an SD/MMC memory card interface, ADC and DACs, and serial interfaces including UART, I<sup>2</sup>C-bus, and I<sup>2</sup>S-bus. Architectural enhancements like multi-channel DMA, processor cache, simultaneous operations on multiple internal buses, and flexible clock generation help ensure that the LPC2880/2888 can handle more demanding applications than many competing devices. The chip can be powered from a single battery, from the USB, or from regulated 1.8 V and 3.3 V.

### 2. Features

#### 2.1 Key features

- ARM7TDMI processor with 8 kB cache, operating at up to 60 MHz

- 1 MB on-chip flash program memory with 128-bit access for high performance

- 64 kB SRAM

- Boot ROM allows execution of flash code, external code, or flash programming via USB

- On-chip DC-to-DC converter can generate all required voltages from a single battery or from USB power

- Multiple internal buses allow simultaneous simple DMA, USB DMA, and program execution from on-chip flash without contention

- External memory controller supports flash, SRAM, ROM, and SDRAM

- Advanced vectored interrupt controller, supporting up to 30 vectored interrupts

- Innovative event router allows interrupt, power-up, and clock-start capabilities from up to 107 sources

- Multi-channel general purpose DMA controller that can be used with most on-chip peripherals as well as for memory-to-memory transfers

- Serial interfaces:

- Hi-Speed or Full-Speed USB 2.0 device (480 Mbit/s or 12 Mbit/s) with on-chip physical layer

- UART with fractional baud rate generation, flow control, IrDA support, and FIFOs

- I<sup>2</sup>C-bus interface

- I<sup>2</sup>S-bus (Inter IC Sound bus) interface for independent stereo digital audio input and output

- SD/MMC memory card interface

- 10-bit ADC with 5-channel input multiplexing

- 16-bit stereo ADC and DACs with gain control

- Advanced clock generation and power control reduce power consumption

- Two 32-bit timers with selectable prescalers

- 8-bit/4-bit LCD interface bus

- Real-Time Clock (RTC) can be clocked by 32 kHz oscillator or another source

- Watchdog timer with interrupt and/or reset capabilities

### 3. Ordering information

| Table 1. Ordering information |          |                                                                                               |          |  |  |  |

|-------------------------------|----------|-----------------------------------------------------------------------------------------------|----------|--|--|--|

| Type number                   | Package  |                                                                                               |          |  |  |  |

|                               | Name     | Description                                                                                   | Version  |  |  |  |

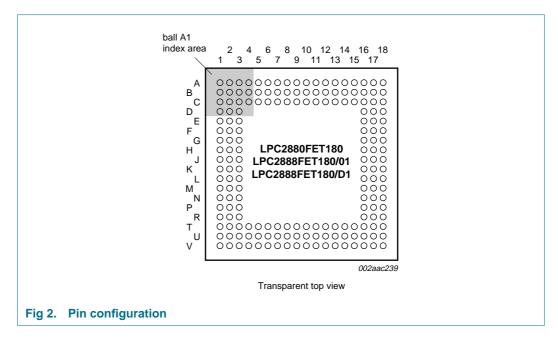

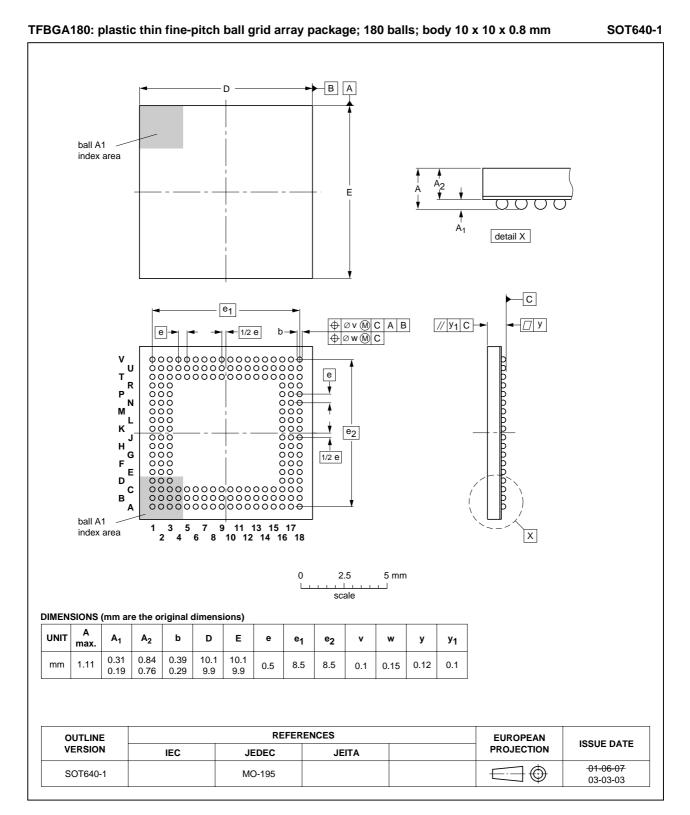

| LPC2880FET180                 | TFBGA180 | plastic thin fine-pitch ball grid array package; 180 balls; body $10 \times 10 \times 0.8$ mm | SOT640-1 |  |  |  |

| LPC2888FET180/01              | TFBGA180 | plastic thin fine-pitch ball grid array package; 180 balls; body $10 \times 10 \times 0.8$ mm | SOT640-1 |  |  |  |

| LPC2888FET180/D1              | TFBGA180 | plastic thin fine-pitch ball grid array package; 180 balls; body $10 \times 10 \times 0.8$ mm | SOT640-1 |  |  |  |

### 3.1 Ordering options

#### Table 2.Ordering options

| Type number      | Flash memory | JTAG interface          | RAM   | Temperature range |

|------------------|--------------|-------------------------|-------|-------------------|

| LPC2880FET180    | -            | enabled                 | 64 kB | –40 °C to +85 °C  |

| LPC2888FET180/01 | 1 MB         | enabled                 | 64 kB | –40 °C to +85 °C  |

| LPC2888FET180/D1 | 1 MB         | disabled <sup>[1]</sup> | 64 kB | –40 °C to +85 °C  |

[1] JTAG interface disabled to provide code read protection. These devices are meant for volume production (no JTAG debugging is possible). The on-chip flash on these devices can only be programmed via USB.

#### 16/32-bit ARM microcontrollers with external memory interface

### 4. Block diagram

#### 16/32-bit ARM microcontrollers with external memory interface

### 5. Pinning information

#### 5.1 Pinning

#### Table 3. Pin allocation table

| Pin | Symbol      | Pin | Symbol                | Pin | Symbol                | Pin | Symbol                |

|-----|-------------|-----|-----------------------|-----|-----------------------|-----|-----------------------|

| Row | Α           |     |                       |     |                       |     |                       |

| 1   | D0/P0[0]    | 2   | D1/P0[1]              | 3   | D3/P0[3]              | 4   | D4/P0[4]              |

| 5   | D6/P0[6]    | 6   | V <sub>SS2(EMC)</sub> | 7   | V <sub>DD2(EMC)</sub> | 8   | STCS1/P1[6]           |

| 9   | RAS/P1[17]  | 10  | MCLKO/P1[14]          | 11  | DQM1/P1[11]           | 12  | BLS0/P1[12]           |

| 13  | A18/P1[2]   | 14  | A15/P0[31]            | 15  | V <sub>SS1(EMC)</sub> | 16  | V <sub>DD1(EMC)</sub> |

| 17  | OE/P1[18]   | 18  | A6/P0[22]             |     | -                     |     | -                     |

| Row | В           |     |                       |     |                       |     |                       |

| 1   | RPO/P1[19]  | 2   | D2/P0[2]              | 3   | LCS/P4[0]             | 4   | D5/P0[5]              |

| 5   | D7/P0[7]    | 6   | D11/P0[11]            | 7   | D13/P0[13]            | 8   | D15/P0[15]            |

| 9   | DYCS/P1[8]  | 10  | CKE/P1[9]             | 11  | STCS2/P1[7]           | 12  | BLS1/P1[13]           |

| 13  | A19/P1[3]   | 14  | A16/P1[0]             | 15  | A13/P0[29]            | 16  | A11/P0[27]            |

| 17  | A9/P0[25]   | 18  | A7/P0[23]             |     | -                     |     | -                     |

| Row | С           |     |                       | ·   |                       |     |                       |

| 1   | LD1/P4[5]   | 2   | LD0/P4[4]             | 3   | LD2/P4[6]             | 4   | D8/P0[8]              |

| 5   | D9/P0[9]    | 6   | D10/P0[10]            | 7   | D12/P0[12]            | 8   | D14/P0[14]            |

| 9   | STCS0/P1[5] | 10  | CAS/P1[16]            | 11  | WE/P1[15]             | 12  | DQM0/P1[10]           |

| 13  | A20/P1[4]   | 14  | A17/P1[1]             | 15  | A14/P0[30]            | 16  | A12/P0[28]            |

| 17  | A10/P0[26]  | 18  | A8/P0[24]             |     | -                     |     | -                     |

| Row | D           |     |                       |     |                       |     |                       |

| 1   | LD4/P4[8]   | 2   | LD3/P4[7]             | 3   | LD5/P4[9]             | 4   | -                     |

LPC2880\_LPC2888\_3

#### 16/32-bit ARM microcontrollers with external memory interface

| Pin alloca          | tion tal | olecontinued            |                        |                          |                                              |                                                |

|---------------------|----------|-------------------------|------------------------|--------------------------|----------------------------------------------|------------------------------------------------|

| nbol                | Pin      | Symbol                  | Pin                    | Symbol                   | Pin                                          | Symbol                                         |

|                     | 14       | -                       | 15                     | -                        | 16                                           | A3/P0[19]                                      |

| P0[20]              | 18       | A5/P0[21]               |                        | -                        |                                              | -                                              |

|                     | ,        |                         |                        |                          |                                              |                                                |

| 1(IO3V3)            | 2        | LD6/P4[10]              | 3                      | LD7/P4[11]               | 4                                            | -                                              |

|                     | 14       | -                       | 15                     | -                        | 16                                           | A0/P0[16]                                      |

| P0[17]              | 18       | A2/P0[18]               |                        | -                        |                                              | -                                              |

|                     |          |                         |                        |                          |                                              |                                                |

| 1(IO)               | 2        | LER/P4[3]               | 3                      | LRS/P4[1]                | 4                                            | -                                              |

|                     | 14       | -                       | 15                     | -                        | 16                                           | DCLKO/P3[3]                                    |

| O/P3[6]             | 18       | WSO                     |                        | -                        |                                              | -                                              |

|                     |          |                         |                        |                          |                                              |                                                |

| 1(CORE)             | 2        | LRW/P4[2]               | 3                      | MCLK/P5[0]               | 4                                            | -                                              |

|                     | 14       | -                       | 15                     | -                        | 16                                           | DATI/P3[0]                                     |

| I/P3[2]             | 18       | BCKO/P3[5]              |                        | -                        |                                              | -                                              |

|                     |          |                         |                        |                          |                                              |                                                |

| 1(CORE1V8)          | 2        | MCMD/P5[1]              | 3                      | MD0/P5[5]                | 4                                            | -                                              |

| . ,                 | 14       | -                       | 15                     | -                        | 16                                           | SCL                                            |

| (I/P3[1]            | 18       | V <sub>SS4(IO)</sub>    |                        | -                        |                                              | -                                              |

|                     |          | (-)                     |                        |                          |                                              |                                                |

| 2/P5[3]             | 2        | MD1/P5[4]               | 3                      | MD3/P5[2]                | 4                                            | -                                              |

|                     | 14       | -                       | 15                     | -                        | 16                                           | MODE2/P2[3]                                    |

| 4                   | 18       | V <sub>DD4(IO3V3)</sub> |                        | -                        |                                              | -                                              |

|                     |          | ()                      |                        |                          |                                              |                                                |

| ō/P6[3]             | 2        | CTS/P6[2]               | 3                      | RXD/P6[0]                | 4                                            | -                                              |

| ••                  | 14       | -                       | 15                     | -                        | 16                                           | P2[0]                                          |

| 1]                  | 18       | MODE1/P2[2]             |                        | -                        |                                              | -                                              |

| •                   |          |                         |                        |                          |                                              |                                                |

| (DAC3V3)            | 2        | VREFP(DAC)              | 3                      | TXD/P6[1]                | 4                                            | -                                              |

| (5/(65/6)           | 14       | -                       | 15                     | -                        | 16                                           | DCDC_GND                                       |

| RT                  | 18       | STOP                    |                        | -                        |                                              | -                                              |

|                     |          |                         |                        |                          |                                              |                                                |

| EFN(DAC)            | 2        | AOUTL                   | 3                      | AOUTR                    | 4                                            | -                                              |

|                     | 14       | -                       | 15                     | -                        | 16                                           | DCDC_V <sub>DDI(3V3)</sub>                     |

| DC_V <sub>BAT</sub> | 18       | DCDC_CLEAN              |                        | -                        |                                              | -                                              |

| BO_ BAI             |          | 0000_022,44             |                        |                          |                                              |                                                |

| <u>1]</u>           | 2        | i.c.[1]                 | 3                      | i.c.[ <u>1]</u>          | 4                                            | -                                              |

| _                   | 14       | -                       | 15                     | -                        | 16                                           | DCDC_V <sub>SS2</sub>                          |

| DC_LX2              |          |                         | 10                     |                          | 10                                           | -                                              |

|                     | 10       | DDO(1V8)                |                        |                          |                                              |                                                |

| - (10)              | 2        | Veerve                  | 3                      | i c [1]                  | Λ                                            | -                                              |

| 6(IO)               |          | ⊻ SS5(IO)               |                        |                          |                                              | -<br>RREF                                      |

| DC_L<br>6(IO)       | X2       | X2 18<br>2<br>14        | 2 V <sub>SS5(IO)</sub> | 2 V <sub>SS5(IO)</sub> 3 | 2 V <sub>SS5(IO)</sub> 3 i.c. <sup>[1]</sup> | 2 V <sub>SS5(IO)</sub> 3 i.c. <sup>[1]</sup> 4 |

Table 3 Pin allocation table continued

Preliminary data sheet

#### 16/32-bit ARM microcontrollers with external memory interface

| Pin | Symbol                  | Pin | Symbol                     | Pin | Symbol                     | Pin | Symbol                     |

|-----|-------------------------|-----|----------------------------|-----|----------------------------|-----|----------------------------|

| 17  | DCDC_LX1                | 18  | $DCDC_V_{SS1}$             |     | -                          |     | -                          |

| Row | R                       |     |                            |     |                            |     |                            |

| 1   | V <sub>DD5(IO3V3)</sub> | 2   | V <sub>DD6(IO3V3)</sub>    | 3   | i.c.[ <u>1]</u>            | 4   | -                          |

| 13  | -                       | 14  | -                          | 15  | -                          | 16  | V <sub>SS2(USB)</sub>      |

| 17  | V <sub>SS1(USB)</sub>   | 18  | DCDC_V <sub>DDO(3V3)</sub> |     | -                          |     | -                          |

| Row | т                       |     |                            |     |                            |     |                            |

| 1   | AINR                    | 2   | i.c.[ <u>1]</u>            | 3   | V <sub>COM(DADC)</sub>     | 4   | AINL                       |

| 5   | JTAG_TDI                | 6   | AIN3                       | 7   | AIN1                       | 8   | X32O                       |

| 9   | V <sub>SS(OSC)</sub>    | 10  | XTALI                      | 11  | V <sub>SS3(INT)</sub>      | 12  | V <sub>SS1(INT)</sub>      |

| 13  | JTAG_TRST               | 14  | RESET                      | 15  | CONNECT                    | 16  | V <sub>SS3(USB)</sub>      |

| 17  | DM                      | 18  | $DCDC_V_{USB}$             |     | -                          |     | -                          |

| Row | U                       |     |                            |     |                            |     |                            |

| 1   | VREF(DADC)              | 2   | VREFP(DADC)                | 3   | V <sub>DD(DADC3V3)</sub>   | 4   | JTAG_SEL                   |

| 5   | AIN4                    | 6   | AIN2                       | 7   | AIN0                       | 8   | V <sub>DD(OSC321V8)</sub>  |

| 9   | V <sub>DD(OSC1V8)</sub> | 10  | V <sub>SS(ADC)</sub>       | 11  | V <sub>SS2(INT)</sub>      | 12  | JTAG_TMS                   |

| 13  | JTAG_TDO                | 14  | VBUS/P7[0]                 | 15  | V <sub>DD1(USB1V8)</sub>   | 16  | V <sub>DD2(USB1V8)</sub>   |

| 17  | DP                      | 18  | V <sub>DD3(USB3V3)</sub>   |     | -                          |     | -                          |

| Row | V                       |     |                            |     |                            |     |                            |

| 1   | VREFN(DADC)             | 2   | V <sub>SS(DADC)</sub>      | 3   | V <sub>DD(DADC1V8)</sub>   | 4   | JTAG_TCK                   |

| 5   | V <sub>DD2(IO3V3)</sub> | 6   | V <sub>SS2(IO)</sub>       | 7   | X32I                       | 8   | V <sub>SS(OSC32)</sub>     |

| 9   | XTALO                   | 10  | V <sub>DD(ADC3V3)</sub>    | 11  | V <sub>DD2(CORE1V8)</sub>  | 12  | V <sub>SS2(CORE)</sub>     |

| 13  | V <sub>SS3(IO)</sub>    | 14  | V <sub>DD3(IO3V3)</sub>    | 15  | V <sub>DD1(FLASH1V8)</sub> | 16  | V <sub>DD2(FLASH1V8)</sub> |

| 17  | V <sub>SS3(CORE)</sub>  | 18  | V <sub>DD4(USB3V3)</sub>   |     | -                          |     | -                          |

#### Table 3. Pin allocation table ...continued

[1] These pins are connected internally and must be left unconnected in an application.

### 5.2 Pin description

| Table 4.               | Pin de  | escription |                       |                                                                                   |

|------------------------|---------|------------|-----------------------|-----------------------------------------------------------------------------------|

| Symbol                 |         | Ball #     | Type <mark>[1]</mark> | Description                                                                       |

| Analog in (            | (dual d | converter) |                       |                                                                                   |

| AINL                   |         | T4         | I                     | analog L input channel                                                            |

| AINR                   |         | T1         |                       | analog R input channel                                                            |

| VCOM(DAE               | DC)     | Т3         | RV                    | ADC common reference voltage and analog output reference voltage combined on-chip |

| VREF(DAD               | C)      | U1         | RV                    | ADC reference voltage                                                             |

| VREFN(DA               | DC)     | V1         | RV                    | ADC negative reference voltage                                                    |

| VREFP(DA               | DC)     | U2         | RV                    | ADC positive reference voltage                                                    |

| V <sub>DD(DADC1V</sub> | 8)      | V3         | Р                     | 1.8 V for dual ADC                                                                |

| V <sub>DD(DADC3V</sub> | 3)      | U3         | Р                     | 3.3 V for dual ADC                                                                |

| V <sub>SS(DADC)</sub>  |         | V2         | Р                     | ground for dual ADC                                                               |

## LPC2880; LPC2888

| <mark>converte</mark> r)<br>U7 | )                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U7                             | /                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | I                                                                                                                    | multiplexed analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| T7                             | I                                                                                                                    | multiplexed analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| U6                             | I                                                                                                                    | multiplexed analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Т6                             | I                                                                                                                    | multiplexed analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| U5                             | 1                                                                                                                    | multiplexed analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V10                            | Р                                                                                                                    | 3.3 V analog supply and reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| U10                            | Р                                                                                                                    | ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| channel)                       |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| M2                             | 0                                                                                                                    | DAC L analog out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| M3                             | 0                                                                                                                    | DAC R analog out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| M1                             | RV                                                                                                                   | negative reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L2                             | RV                                                                                                                   | positive reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L1                             | Ρ                                                                                                                    | 3.3 V for DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| H17                            | FI                                                                                                                   | DAI bit clock; 5 V tolerant GPIO pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| G16                            | FI                                                                                                                   | DAI serial data input; 5 V tolerant GPIO pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| G17                            | FI                                                                                                                   | DAI word select; 5 V tolerant GPIO pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G18                            | FO                                                                                                                   | DAO bit clock; 5 V tolerant GPIO pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F17                            | FO                                                                                                                   | DAO serial data output; 5 V tolerant GPIO pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F16                            | FO                                                                                                                   | $256 \times clock output; 5 V tolerant GPIO pin$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| F18                            | 0                                                                                                                    | DAO word select; 5 V tolerant pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ers                            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| L17                            | I                                                                                                                    | DC-to-DC converter activation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| L18                            | I                                                                                                                    | DC-to-DC converter deactivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| M18                            | Ρ                                                                                                                    | reference circuit ground, not connected to substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| L16                            | Ρ                                                                                                                    | DC-to-DC converter main ground and substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P17                            | Ρ                                                                                                                    | connect to external coil for DC/DC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| N17                            | Ρ                                                                                                                    | connect to external coil for DC/DC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M17                            | Ρ                                                                                                                    | connect to battery +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| M16                            | Р                                                                                                                    | DC/DC1 3.3 V input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| N18                            | Ρ                                                                                                                    | DC/DC2 1.8 V output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| R18                            | Ρ                                                                                                                    | DC/DC1 3.3 V output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P18                            | Ρ                                                                                                                    | ground for DC/DC1, not connected to substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| N16                            | Ρ                                                                                                                    | ground for DC/DC2, not connected to substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | G17<br>G18<br>F17<br>F16<br>F18<br>Cers<br>L17<br>L18<br>M18<br>L16<br>P17<br>N17<br>M17<br>M17<br>M16<br>N18<br>R18 | U10       P         M2       O         M3       O         M1       RV         L2       RV         L1       P         G16       FI         G17       FI         G18       FO         F17       FO         F18       O         Cers       I         L17       I         L18       I         M18       P         L16       P         P17       P         M18       P         L16       P         P17       P         M18       P         L16       P         P17       P         M17       P         M17       P         M16       P         P18       P         N16       P |

## LPC2880; LPC2888

#### 16/32-bit ARM microcontrollers with external memory interface

| Symbol           | Ball #       | Type <sup>[1]</sup> | Description                                                          |

|------------------|--------------|---------------------|----------------------------------------------------------------------|

| External memo    | ory interfac | e                   |                                                                      |

| D0/P0[0]         | A1           | FI                  | external memory data bus, low byte (I/O); GPIO pins                  |

| D1/P0[1]         | A2           |                     |                                                                      |

| D2/P0[2]         | B2           |                     |                                                                      |

| D3/P0[3]         | A3           |                     |                                                                      |

| D4/P0[4]         | A4           |                     |                                                                      |

| D5/P0[5]         | B4           |                     |                                                                      |

| D6/P0[6]         | A5           |                     |                                                                      |

| D7/P0[7]         | B5           |                     |                                                                      |

| D8/P0[8]         | C4           | FI                  | external memory data bus, high byte (I/O); GPIO pins                 |

| D9/P0[9]         | C5           |                     |                                                                      |

| D10/P0[10]       | C6           |                     |                                                                      |

| D11/P0[11]       | B6           |                     |                                                                      |

| D12/P0[12]       | C7           |                     |                                                                      |

| D13/P0[13]       | B7           |                     |                                                                      |

| D14/P0[14]       | C8           |                     |                                                                      |

| D15/P0[15]       | B8           |                     |                                                                      |

| A0/P0[16]        | E16          | FO                  | address bus for SDRAM and static memory; GPIO pins                   |

| A1/P0[17]        | E17          |                     |                                                                      |

| A2/P0[18]        | E18          |                     |                                                                      |

| A3/P0[19]        | D16          |                     |                                                                      |

| A4/P0[20]        | D17          |                     |                                                                      |

| A5/P0[21]        | D18          |                     |                                                                      |

| A6/P0[22]        | A18          |                     |                                                                      |

| A7/P0[23]        | B18          |                     |                                                                      |

| A8/P0[24]        | C18          |                     |                                                                      |

| A9/P0[25]        | B17          |                     |                                                                      |

| A10/P0[26]       | C17          |                     |                                                                      |

| A11/P0[27]       | B16          |                     |                                                                      |

| A12/P0[28]       | C16          |                     |                                                                      |

| A13/P0[29]       | B15          |                     |                                                                      |

| A14/P0[30]       | C15          |                     |                                                                      |

| A15/P0[31]       | A14          | FO                  | address bus for static memory; GPIO pins                             |

| A16/P1[0]        | B14          |                     |                                                                      |

| A17/P1[1]        | C14          |                     |                                                                      |

| A18/P1[2]        | A13          |                     |                                                                      |

| A19/P1[3]        | B13          |                     |                                                                      |

| A20/P1[4]        | C13          |                     |                                                                      |

| BLS0/P1[12]      | A12          | FO                  | byte lane select for D[7:0], active LOW for static memory; GPIO pin  |

| BLS1/P1[13]      | B12          | FO                  | byte lane select for D[15:8], active LOW for static memory; GPIO pin |

| CAS/P1[16]       | C10          | FO                  | column address strobe, active LOW for SDRAM; GPIO pin                |

| PC2880_LPC2888_3 |              |                     | © NXP B.V. 2008. All rights rese                                     |

Preliminary data sheet

## LPC2880; LPC2888

#### 16/32-bit ARM microcontrollers with external memory interface

| Symbol                         | Ball # | continued | Description                                                                              |

|--------------------------------|--------|-----------|------------------------------------------------------------------------------------------|

| CKE/P1[9]                      | B10    | FO        | clock enable; active HIGH for SDRAM; GPIO pin                                            |

| DQM0/P1[10]                    | C12    | FO        | data mask output for D[7:0], active HIGH for SDRAM; GPIO pin                             |

| DQM1/P1[11]                    | A11    | FO        | data mask output for D[15:8], active HIGH for SDRAM; GPIO pin                            |

| DYCS/P1[8]                     | B9     | FO        | chip select, active LOW for SDRAM; GPIO pin                                              |

| MCLKO/P1[14]                   | A10    | FO        | clock for SDRAM and SyncFlash memory; GPIO pin                                           |

| OE/P1[18]                      | A17    | FO        | output enable, active LOW for static memory; GPIO pin                                    |

| RAS/P1[17]                     | A9     | FO        | row address strobe, active LOW for SDRAM; GPIO pin                                       |

| RPO/P1[19]                     | B1     | FO        | reset power-down, active LOW for SyncFlash memory; GPIO pin                              |

| STCS0/P1[5]                    | C9     | FO        | chip select, active LOW for static memory bank 0; GPIO pin                               |

| STCS1/P1[6]                    | A8     | FO        | chip select, active LOW for static memory bank 1; GPIO pin                               |

| STCS2/P1[7]                    | B11    | FO        | chip select, active LOW for static memory bank 2; GPIO pin                               |

| WE/P1[15]                      | C11    | FO        | write enable, active LOW for SDRAM and static memory; GPIO pin                           |

| GPIO and mode                  |        |           | , , ,                                                                                    |

| MODE1/P2[2]                    | K18    | FI        | start-up mode pin 1 (pull-down); 5 V tolerant GPIO pin                                   |

| MODE2/P2[3]                    | J16    | FI        | start-up mode pin 2 (pull-down); 5 V tolerant GPIO pin                                   |

| P2[0]                          | K16    | FI        | 5 V tolerant GPIO pin                                                                    |

| P2[1]                          | K17    | FI        | 5 V tolerant GPIO pin                                                                    |

| l <sup>2</sup> C-bus interface |        |           |                                                                                          |

| SCL                            | H16    | I/O       | serial clock (input/open-drain output); 5 V tolerant pin                                 |

| SDA                            | J17    | I/O       | serial data (input/open-drain output); 5 V tolerant pin                                  |

| JTAG interface                 |        |           |                                                                                          |

| JTAG_SEL                       | U4     | 1         | JTAG selection (pull-down); 5 V tolerant pin                                             |

| JTAG_TCK                       | V4     | 1         | JTAG reset input (pull-down); 5 V tolerant pin                                           |

| JTAG_TDI                       | T5     | -         | JTAG data input (pull-up); 5 V tolerant pin                                              |

| JTAG_TMS                       | U12    | 1         | JTAG mode select input (pull-up); 5 V tolerant pin                                       |

| JTAG_TRST                      | T13    | 1         | JTAG reset input (pull-down); 5 V tolerant pin                                           |

| JTAG_TDO                       | U13    | 0         | JTAG data output; 5 V tolerant pin                                                       |

| LCD interface                  |        | -         |                                                                                          |

| LCS/P4[0]                      | B3     | FO        | chip select to LCD device, programmable polarity; 5 V tolerant GPIO pin                  |

| LD0/P4[4]                      | C2     | FO        | data bus to/from LCD (I/O) or 5 V tolerant GPIO pins                                     |

| LD1/P4[5]                      | C1     | FO        |                                                                                          |

| LD2/P4[6]                      | C3     | FO        |                                                                                          |

| LD3/P4[7]                      | D2     | FO        |                                                                                          |

| LD4/P4[8]                      | D1     | FO        |                                                                                          |

| LD5/P4[9]                      | D3     | FO        |                                                                                          |

| LD6/P4[10]                     | E2     | FO        |                                                                                          |

| LD7/P4[11]                     | E3     | FO        |                                                                                          |

| LER/P4[3]                      | F2     | FO        | 6800 E or 8080 RD or 5 V tolerant GPIO pin                                               |

| LRS/P4[1]                      | F3     | FO        | 'HIGH' data register select, 'LOW' instruction register select, or 5 V tolerant GPIO pin |

| LRW/P4[2]                      | G2     | FO        | 6800 W/R or 8080 WR or 5 V tolerant GPIO pin                                             |

**Preliminary data sheet**

## LPC2880; LPC2888

| Symbol                    | Ball #   | Type <sup>[1]</sup> | Description                                                                                                  |

|---------------------------|----------|---------------------|--------------------------------------------------------------------------------------------------------------|

| Memory card in            | nterface |                     |                                                                                                              |

| MCMD/P5[1]                | H2       | FI                  | command (I/O); 5 V tolerant GPIO pin                                                                         |

| MD0/P5[5]                 | H3       | FI                  | data bus from/to SD/MCI card (I/O); 5 V tolerant GPIO pin                                                    |

| MD1/P5[4]                 | J2       | FI                  | data bus from/to SD/MCI card (I/O); 5 V tolerant GPIO pin                                                    |

| MD2/P5[3]                 | J1       | FI                  | data bus from/to SD/MCI card (I/O); 5 V tolerant GPIO pin                                                    |

| MD3/P5[2]                 | J3       | FI                  | data bus from/to SD/MCI card (I/O); 5 V tolerant GPIO pin                                                    |

| MCLK/P5[0]                | G3       | FO                  | MCI clock output; 5 V tolerant GPIO pin                                                                      |

| Oscillator (32.7          | '68 kHz) |                     |                                                                                                              |

| X32I                      | V7       | I                   | 32.768 kHz oscillator input                                                                                  |

| X32O                      | T8       | 0                   | 32.768 kHz oscillator output                                                                                 |

| V <sub>DD(OSC321V8)</sub> | U8       | Р                   | 1.8 V                                                                                                        |

| V <sub>SS(OSC32)</sub>    | V8       | Р                   | ground                                                                                                       |

| Oscillator (mai           | n)       |                     |                                                                                                              |

| XTALI                     | T10      | I                   | main oscillator input                                                                                        |

| XTALO                     | V9       | 0                   | main oscillator output                                                                                       |

| V <sub>DD(OSC1V8)</sub>   | U9       | Р                   | 1.8 V                                                                                                        |

| V <sub>SS(OSC)</sub>      | Т9       | Р                   | ground                                                                                                       |

| Reset                     |          |                     |                                                                                                              |

| RESET                     | T14      | I                   | master reset, active LOW; 5 V tolerant pin                                                                   |

| UART                      |          |                     |                                                                                                              |

| CTS/P6[2]                 | K2       | FI                  | clear to send or transmit flow control, active LOW; 5 V tolerant GPIO pin                                    |

| RXD/P6[0]                 | K3       | FI                  | serial input; 5 V tolerant GPIO pin                                                                          |

| RTS/P6[3]                 | K1       | FO                  | request to send or receive flow control, active LOW; 5 V tolerant GPIO pin                                   |

| TXD/P6[1]                 | L3       | FO                  | serial output; 5 V tolerant GPIO pin                                                                         |

| USB interface             |          |                     |                                                                                                              |

| CONNECT                   | T15      | Ρ                   | used for signalling speed capability; for high-speed USB, connect an externa 1.5 $k\Omega$ resistor to 3.3 V |

| DM                        | T17      | I/O                 | negative USB data line                                                                                       |

| DP                        | U17      | I/O                 | positive USB data line                                                                                       |

| RREF                      | P16      | Р                   | transceiver reference; connect an external 12 k $\Omega$ 1 % resistor to ground                              |

| VBUS/P7[0]                | U14      | FI                  | USB supply detection; 5 V tolerant GPIO pin                                                                  |

| V <sub>DD1(USB1V8)</sub>  | U15      | Р                   | analog 1.8 V                                                                                                 |

| V <sub>DD2(USB1V8)</sub>  | U16      | Р                   | analog 1.8 V                                                                                                 |

| V <sub>DD3(USB3V3)</sub>  | U18      | Р                   | analog 3.3 V                                                                                                 |

| V <sub>DD4(USB3V3)</sub>  | V18      | Р                   | analog 3.3 V                                                                                                 |

| V <sub>SS1(USB)</sub>     | R17      | Р                   | analog ground                                                                                                |

| V <sub>SS2(USB)</sub>     | R16      | Р                   | analog ground                                                                                                |

| V <sub>SS3(USB)</sub>     | T16      | Р                   | analog ground                                                                                                |

## LPC2880; LPC2888

#### 16/32-bit ARM microcontrollers with external memory interface

| Table 4.               | Pin des       | scription . | continued           |                                               |

|------------------------|---------------|-------------|---------------------|-----------------------------------------------|

| Symbol                 |               | Ball #      | Type <sup>[1]</sup> | Description                                   |

| Digital po             | wer and       | ground      |                     |                                               |

| V <sub>DD1(CORE</sub>  | 1V8)          | H1          | Р                   | 1.8 V for internal RAM and ROM                |

| VDD1(FLASH             | I1V8)         | V15         | Р                   | 1.8 V for internal flash memory               |

| V <sub>DD1(EMC)</sub>  |               | A16         | Р                   | 1.8 V or 3.3 V for external memory controller |

| V <sub>DD1(IO3V3</sub> | )             | E1          | Р                   | 3.3 V for peripherals                         |

| V <sub>DD2(CORE</sub>  | 1V8)          | V11         | Р                   | 1.8 V for core                                |

| V <sub>DD2(EMC)</sub>  |               | A7          | Р                   | 1.8 V or 3.3 V for external memory controller |

| VDD2(FLASH             | <b>1</b> 1∨8) | V16         | Р                   | 1.8 V for internal flash memory               |

| V <sub>DD2(IO3V3</sub> | )             | V5          | Р                   | 3.3 V for peripherals                         |

| V <sub>DD3(IO3V3</sub> | )             | V14         | Р                   | 3.3 V for peripherals                         |

| V <sub>DD4(IO3V3</sub> | )             | J18         | Р                   | 3.3 V for peripherals                         |

| V <sub>DD5(IO3V3</sub> | )             | R1          | Р                   | 3.3 V for peripherals                         |

| V <sub>DD6(IO3V3</sub> | )             | R2          | Р                   | 3.3 V for peripherals                         |

| V <sub>SS1(CORE)</sub> | )             | G1          | Р                   | ground for internal RAM and ROM               |

| V <sub>SS1(EMC)</sub>  |               | A15         | Р                   | ground for external memory controller         |

| V <sub>SS1(INT)</sub>  |               | T12         | Р                   | ground for other internal blocks              |

| V <sub>SS1(IO)</sub>   |               | F1          | Р                   | ground for peripherals                        |

| V <sub>SS2(CORE)</sub> |               | V12         | Р                   | ground for core                               |

| V <sub>SS2(EMC)</sub>  |               | A6          | Р                   | ground for external memory controller         |

| V <sub>SS2(INT)</sub>  |               | U11         | Р                   | ground for other internal blocks              |

| V <sub>SS2(IO)</sub>   |               | V6          | Р                   | ground for peripherals                        |

| V <sub>SS3(CORE)</sub> | )             | V17         | Р                   | ground for core, substrate, flash             |

| V <sub>SS3(INT)</sub>  |               | T11         | Р                   | ground for other internal blocks              |

| V <sub>SS3(IO)</sub>   |               | V13         | Р                   | ground for peripherals                        |

| V <sub>SS4(IO)</sub>   |               | H18         | Р                   | ground for peripherals                        |

| V <sub>SS5(IO)</sub>   |               | P2          | Р                   | ground for peripherals                        |

| V <sub>SS6(IO)</sub>   |               | P1          | Р                   | ground for peripherals                        |

[1] I = input; O = output; I/O = input/output; RV = reference voltage; FI = functional input; FO = functional output; P = power or ground

### 6. Functional description

#### 6.1 Architectural overview

The LPC2880/2888 includes an ARM7TDMI CPU with an 8 kB cache, an AMBA AHB interfacing to high-speed on-chip peripherals and internal and external memory, and four AMBA APBs for connection to other on-chip peripheral functions.

The LPC2880/2888 includes a multi-layer AHB and four separate APBs, in order to minimize interference between the USB controller, other DMA operations, and processor activity. Bus masters include the ARM7 itself, the USB block, and the general purpose DMA controller.

Lower speed peripheral functions are connected to the APBs. The four AHB-to-APB bridges interface the APBs to the AHB.

#### 6.1.1 ARM7TDMI processor

The ARM7TDMI is a general purpose 32-bit microprocessor that offers high performance and very low power consumption. The ARM architecture is based on RISC principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed CISCs. This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI processor also employs a unique architectural strategy known as Thumb, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM7TDMI processor has two instruction sets:

- The standard 32-bit ARM instruction set.

- A 16-bit Thumb instruction set.

The Thumb set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide down to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

The ARM7TDMI processor is described in detail on the ARM web site.

#### 6.1.2 On-chip flash memory system

The LPC2880/2888 includes a 1 MB flash memory system. This memory may be used for both code and data storage. Programming of the flash memory may be accomplished in several ways. It may be programmed In System via the USB port. The application program may also erase and/or program the flash while the application is running, allowing a great degree of flexibility for data storage field firmware upgrades, etc.

The flash is 128 bit wide and includes buffering to allow 3 out of 4 sequential read operations to operate without wait states.

#### 6.1.3 On-chip SRAM

The LPC2880/2888 includes 64 kB of SRAM that may be used for code and/or data storage.

#### 6.1.4 On-chip ROM

The LPC2880/2888 includes an on-chip ROM that contains boot code. Execution begins in on-chip ROM after a reset.

The boot code in this ROM reads the state of the mode inputs and accordingly does one of the following:

- Starts execution in internal flash

- Starts execution in external memory

- · Performs a hardware self-test, or

- Downloads code from the USB interface into on-chip RAM and transfers control to the downloaded code

#### 6.2 Memory map

The LPC2880/2888 memory map incorporates several distinct regions, as shown in Figure 3. When an application is running, the CPU interrupt vectors are remapped to allow them to reside in on-chip SRAM.

## LPC2880; LPC2888

| 4.0 GB            | reserved                     | 0x9000 0000 to 0xFFFF FFFF | 0xFFFF FFFF<br>0x9000 0000 |

|-------------------|------------------------------|----------------------------|----------------------------|

| peripherals       | includes AHB and 4 APB buses | 0x8000 0000 to 0x8FFF FFFF | 0x8FFF FFFF<br>0x8000 0000 |

| 2.0 GB            | reserved                     | 0x5400 0000 to 0x7FFF FFFF | 0x7FFF FFFF                |

|                   | dynamic memory bank 0, 64 MB | 0x5000 0000 to 0x53FF FFFF |                            |

|                   | reserved                     | 0x4820 0000 to 0x4FFF FFFF |                            |

| external memory   | static memory bank 2, 2 MB   | 0x4800 0000 to 0x481F FFFF |                            |